メモリの高速アクセスには、CPUと主記憶の速度差を埋めるキャッシュメモリの導入、メモリを分割して並列処理するメモリインターリーブ、DDR5のような高速なメモリの採用が有効です。これらはCPUが必要なデータへのアクセス回数と時間を短縮し、システム全体の処理速度を向上させます。

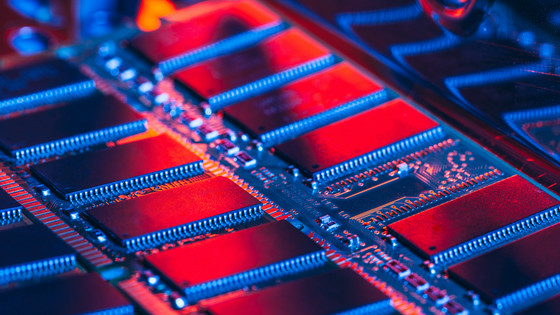

画像参照:https://news.livedoor.com/article/detail/30193294/

キャッシュメモリ

キャッシュメモリは、CPUとメインメモリ(主記憶装置)の間に配置される、高速かつ小容量のメモリです。CPUが頻繁に使用するデータや命令を一時的に保持することで、低速なメインメモリへのアクセス回数を減らし、パソコンやスマホの処理速度を高速化する役割を果たします。

主な特徴と役割

- 処理速度の高速化: CPUの動作速度とメインメモリの速度差(ボトルネック)を埋め、CPUの待ち時間を減らします。

- 高速・小容量: SRAMという高速な記憶素子で構成されており、アクセス速度はメインメモリより非常に速いですが、容量は小さくコストが高い。

- 配置: 主にCPUの内部に配置され、データを高速に転送します。

- 階層構造: 速度と容量のバランスを取るため、L1(1次)、L2(2次)、L3(3次)キャッシュのように階層化されています。

- L1キャッシュ: CPUに最も近く、最も高速で容量は最小。

- L2/L3キャッシュ: L1よりも少し遅いが、大容量。

動作の仕組み

CPUはデータを読み込む際、まずキャッシュメモリを探します(キャッシュヒット)。データがあれば高速に処理できますが、なければ(キャッシュミス)、低速なメインメモリへアクセスし、データをキャッシュメモリへコピーします。

注意点

キャッシュメモリは自動的にデータ管理を行うため、基本的にプログラム側が意識する必要はありませんが、容量には限界があり、古いデータは自動的に削除(上書き)されます。

実行メモリアクセス時間

実行メモリアクセス時間は、キャッシュメモリと主記憶(メインメモリ)を持つシステムにおいて、CPUがデータを取得する際にかかる平均的なアクセス時間のことです。高速なキャッシュのヒット率を考慮し、「キャッシュ時間×ヒット率 + 主記憶時間×(1-ヒット率)」の式で算出します。

実効アクセス時間の計算式

実効アクセス時間=(キャッシュ時間×ヒット率)+(主記憶時間×(1−ヒット率))

- キャッシュメモリのアクセス時間: データがキャッシュにある場合。高速(数ナノ秒)。

- 主記憶のアクセス時間: データがキャッシュになく、主記憶まで探しに行く場合(低速)。

- ヒット率: CPUが必要とするデータがキャッシュメモリに存在している確率。

計算例

キャッシュメモリへのアクセス時間が2ナノ秒、主記憶へのアクセス時間が100ナノ秒、ヒット率が90%(0.9)の場合。

実効アクセス時間=(2×0.9)+(100×(1−0.9))=1.8+10=11.8ナノ秒

特徴

- ヒット率が高いほど短くなる: キャッシュメモリを効果的に活用できれば、実効アクセス時間はキャッシュの速さに近づく。

- 平均時間である: 毎回固定の時間ではなく、キャッシュへのヒット有無によって高速な時と低速な時がある。

キャッシュメモリは主記憶よりも高速であるため、この技術によりコンピュータ全体としての処理速度が向上する。

ライトスルー

ライトスルーは、CPUがキャッシュメモリにデータを書き込む際、同時にメインメモリにも書き込む方式。キャッシュとメモリの内容が常に一致するためデータ整合性が高く、システムが停止してもデータが失われにくい安全な方式である。一方で、書き込みのたびに低速なメインメモリへのアクセスが発生するため、ライトバック方式に比べて書き込み速度は劣る。

主な特徴と利点・欠点

- 整合性(一貫性): キャッシュとメモリの内容が常に一致する(データ喪失リスクが低い)。

- 実装: 制御回路が単純で実装しやすい。

- 速度: 書き込み時に常に低速なメモリへのアクセスが発生するため、遅い。

- 用途: データの信頼性が最優先されるシステムに適している。

ライトバック

ライトバックは、CPUがデータをキャッシュメモリに書き込む際、メインメモリへはすぐ反映させず、キャッシュからデータが追い出される時にまとめて更新する方式です。高速なキャッシュのみを更新するため書き込み性能が大幅に向上するが、構造は複雑になる。

主な特徴

- 高速な処理: CPUが低速なメインメモリを待たずに処理を終えられる。

- ダーティビット: キャッシュ内のデータが更新された際、変更済みを示すフラグ(ダーティビット)を立てる。

- 書込みのタイミング: キャッシュが満杯になり、古いデータが追い出される(ライトバック/フラッシュ)際に、メインメモリへ一括して書き戻す。

- デメリット: キャッシュとメモリのデータが必ずしも一致しない。停電などでデータが失われるリスクがある。

ライトスルー方式との違い

| 特徴 | ライトバック | ライトスルー |

|---|---|---|

| 書き込み先 | キャッシュのみ | キャッシュ + メインメモリ |

| 高速性 | 非常に高速 | 低速 |

| 整合性 | 一時的に不一致が生じる | 常に一致する |

| 複雑さ | 高い | 低い |

ライトバックは、頻繁に同じデータを書き換える処理(「同じデータへ何度も上書き」)が連続する場合に、メモリへのアクセス回数を削減し、システム全体のパフォーマンスを最大化するのに適している。

メモリインタリーブ

メモリインタリーブは、メインメモリを「バンク」と呼ばれる複数の領域に分割し、CPUがそれらに並列アクセスすることで、メモリの読み書きを高速化する技術。連続するデータを異なるバンクに配置し、一方のアクセス遅延時間に他方へアクセスする手法で、主にサーバーや高速性が求められるパソコンで利用される。

特徴と利点

- 高速アクセス: 複数のバンクへ同時または交互にアクセスするため、見かけ上のアクセス時間を短縮できる。

- 安価なメモリで高速化: レイテンシが長い(遅い)安価なメモリでも、並列化により高い処理性能が得られる。

- 応用: 「デュアルチャネル」や「トリプルチャネル」は、この技術を応用してメモリスロットを分けて使用する手法である。

難点

- 制御の複雑化: メモリコントローラが複雑になり、設計コストや部品コストが上昇する。

- 増設の制限: 高性能を発揮するためには、同じ容量・規格のメモリモジュールを複数枚単位で装着する必要がある。

動作イメージ

データアドレスを0, 1, 2, 3…と順にアクセスする場合、1番目のデータをバンクA、2番目をバンクBに配置し、Aにアクセスしている間にBの準備を行う、という動作を繰り返す。

コメント