機械語命令(マシン語命令)とは、コンピュータのCPUが直接理解・実行できる、0と1のビット列で表されたコンピュータの最も基本的な命令です。演算、データ転送、分岐などの CPU の動作を指示するもので、人間が使うプログラミング言語(C言語など)は最終的にこの機械語に変換されて実行されます。

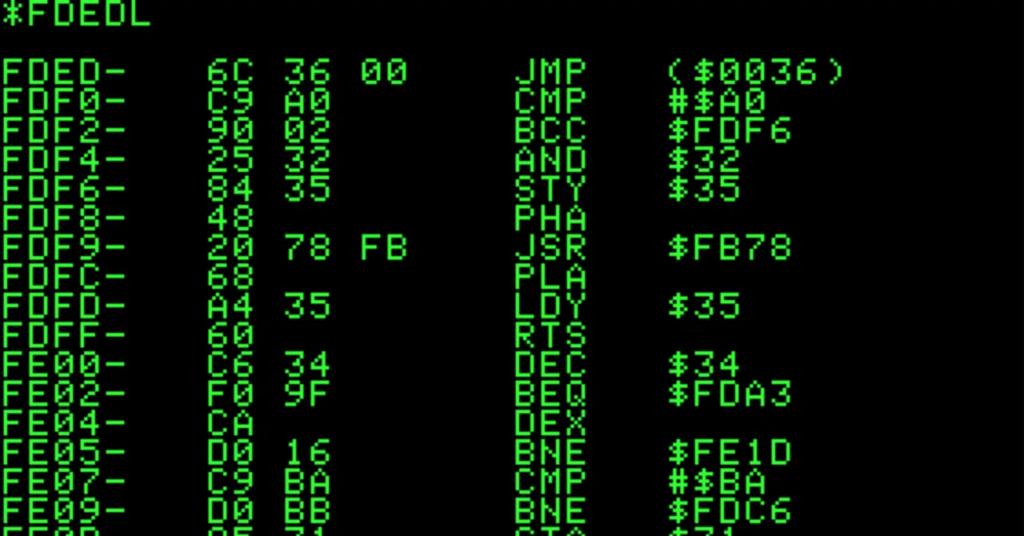

画像参照:https://note.com/kazushinakamura/n/n0977f617973a

機械語命令の種類

機械語命令は、CPUが直接実行する基本命令のことで、主に算術・論理演算命令(加減乗除、AND/ORなど)、データ転送命令(メモリとレジスタ間の移動:LD, ST, MOVなど)、比較命令(大小比較)、分岐命令(処理の順序変更)、シフト命令(ビットの移動)など、機能別に分類されます。これらは、アセンブリ言語(MOV, ADD, JMPなど)を通じて表現され、最終的にCPUが理解できる「0」と「1」のビット列(機械語)に変換されます。

主な機械語命令の種類

- 算術演算命令

- 加算 (ADD)、減算 (SUB)、乗算 (MUL)、除算 (DIV) など、数値計算を行う。

- 論理演算命令

- AND (論理積)、OR (論理和)、XOR (排他的論理和)、NOT (否定) など、ビット単位の論理演算を行う。

- データ転送命令

- メモリとレジスタ間でデータを移動させる命令。例:

LD(Load): メモリからレジスタへデータをロードする。ST(Store): レジスタからメモリへデータを保存する。MOV: レジスタ間やメモリとレジスタ間でデータを移動させる。

- メモリとレジスタ間でデータを移動させる命令。例:

- 比較命令

- 2つの値を比較し、その結果をフラグレジスタにセットする(例: 等しい、より大きいなど)。

- 分岐命令

- 条件に応じてプログラムの実行フローを変更する。例:

JMP(無条件分岐)、JE(等しい場合分岐) など。

- 条件に応じてプログラムの実行フローを変更する。例:

- シフト命令

- レジスタ内のビット列を左または右に移動させる(数値の2倍/半分にする効果も)。

- アドレス指定命令

LAD(Load Address) のように、メモリのアドレス値をレジスタにロードする命令。

アセンブリ言語との関係

- 機械語はコンピュータが直接理解する0と1の羅列。

- アセンブリ言語は、機械語命令に人間が読みやすい略号(ニーモニック)をつけたもの(例:

ADD、MOV)。 - これらの命令が、CPUのアーキテクチャ(x86, ARMなど)に応じて具体的なビットパターン(機械語コード)に変換され、実行されます。

機械語命令の構成

機械語命令は、CPUが直接理解・実行できる0と1の二進数(ビット)の列で構成されています。主にオペコード(操作コード)とオペランド(操作対象)の2つの要素で構成され、CPUのアーキテクチャごとに固有の形式を持っています。

基本構成

多くの機械語命令は、大きく分けて以下の部分で構成されます。

- オペコード

- CPUに「何をさせるか」を指示する命令コード(演算、データ移動、ジャンプなど)。

- 例: 加算(ADD)、転送(MOV)など。

- オペランド

- オペコードで指定された動作の「対象となるデータや住所」。

- 具体的な数値(即値)、レジスタ番号、メモリのアドレスなどが指定される。

- アドレッシングモード

- オペランドがどこにあるか(レジスタ直接か、メモリのどこか)を規定する情報。

命令の具体例とイメージ

命令は固定長(例: 32ビットすべて)または可変長で構成されます。

例:MOV 命令 (データの移動)10110000 00000001 (8ビット+8ビットの例)

- 10110000: オペコード(MOVを意味する)

- 00000001: オペランド(値「1」)

MIPS (RISCアーキテクチャ) の例 (R型命令 – 32ビット)

- opcode (6ビット): 操作の種類

- rs (5ビット): 第1ソースレジスタ

- rt (5ビット): 第2ソースレジスタ

- rd (5ビット): デスティネーションレジスタ(結果格納先)

- shamt (5ビット): シフト量

- funct (6ビット): 詳細な機能

命令の種類(アドレッシングによる分類)

オペランドの数や位置によって、以下の形式があります。

- 0アドレス命令: スタックなどを使用し、オペランドを持たない命令。

- 1アドレス命令: アキュムレータ(AC)と1つのメモリアドレスを使用。

- 2アドレス命令: 「宛先」と「源(ソース)」を指定。

- 3アドレス命令: 2つの「源」と1つの「宛先」を指定。

まとめ

機械語命令は、CPUの回路レベルでデコード(解読)されるため、人間が読むのには適していませんが、効率的にハードウェアを動かすために設計されています。この構造は、Intelのx86やARM、RISC-Vなど、CPUのアーキテクチャごとに異なります。

アドレッシングモード

アドレッシングモードとは、コンピュータのCPUが命令を実行する際に、処理対象のデータ(オペランド)がメモリやレジスタのどこにあるか(アドレス)を指定する方式のことです。直接アドレスを指定する「直接アドレッシング」や、アドレスが格納された場所を指定する「間接アドレッシング」、アドレスに定数やレジスタ値を加算する「アドレス修飾」など、様々な方法があり、プログラムの柔軟性や効率を高めます。

主なアドレッシングモードの種類

- 即値アドレッシング : 命令自体にデータが直接含まれる方式(メモリのアドレスは指定しない)。

- 直接アドレッシング: 命令のアドレス部に書かれた値をそのままメモリのアドレスとして使う方式。

- 間接アドレッシング: 命令のアドレス部に書かれたメモリ位置に、さらに目的のデータのアドレスが書かれている方式。

- レジスタ直接アドレッシング : データがレジスタに直接格納されている方式。

- レジスタ間接アドレッシング : レジスタに格納された値がメモリ上のアドレスを示す方式。

- アドレス修飾 :

- ベースアドレス指定: ベースレジスタの値にオフセット(変位)を加算。

- インデックス指定: インデックスレジスタの値にオフセットを加算。

- PC相対アドレッシング: プログラムカウンタ(PC)の値にオフセットを加算し、分岐などに利用。

- スケールド・インデックス・モード: インデックスレジスタの値にデータサイズを掛けたもの(スケール)とオフセットを加算する、より複雑なモード。

オフセット

基準位置からの相対的な差や距離のことを指します。

アドレッシングモードの重要性

- 柔軟性: データの配置方法が多様になり、複雑なデータ構造やプログラミングパターンに対応しやすくなります。

- 効率: 適切なモードを選ぶことで、メモリへのアクセス回数を減らし、プログラムの実行速度を向上させられます。

- CPU設計: RISCアーキテクチャでは、高速化のためにアドレッシングモードの種類を限定する傾向があります。

即値アドレッシング

即値アドレッシングとは、CPUの命令において、処理対象のデータそのもの(即値)を命令のオペランド部に直接記述し、メモリを参照せずにその値を使って処理を行うアドレス指定方式です。メモリへのアクセスが不要なため最も高速ですが、プログラム中に固定データとして埋め込まれるため、後から値を変更できない定数などに利用されます。

仕組み

- 命令形式: 命令コードの後に、データそのもの(例:数値「1000」)が直接記述されます。

- データ取得: CPUはメモリに問い合わせることなく、命令内のその値(即値)を直接読み取って利用します。

特徴

- 高速: メモリ参照のオーバーヘッドがないため、非常に高速に処理できます。

- 定数向け: 処理中に値が変わらない定数(例:最大値、初期値)の指定に適しています。

- 柔軟性なし: プログラム実行中にデータを変更したり、外部からの入力を直接扱ったりすることはできません。

直接アドレッシング

直接アドレッシングとは、CPUが命令を実行する際、命令のオペランド部(アドレス部)に記述された番地(アドレス)を、データが格納されているメモリの場所として直接使用する方式です。この方式では、メモリ上の特定のアドレスに直接アクセスしてデータを読み書きするため、高速で効率的ですが、プログラムの再配置が難しいという特徴もあります。

仕組み

- 命令のオペランド部: 命令コードの一部であるオペランド(アドレス部)に、目的のデータが置かれているメモリの実効アドレス(有効アドレス)が直接書かれています。

- 直接アクセス: CPUは、オペランド部に書かれたアドレス値をそのままメモリの番地として利用し、その場所からデータを取得したり、データを書き込んだりします。

例

- 命令のアドレス部に「20」と書かれていれば、メモリの20番地にあるデータを直接参照します。

利点

- 高速: アドレス変換の必要がなく、直接メモリにアクセスできるため、処理が速いです。

- シンプル: 実装が比較的単純です。

欠点

- 再配置の困難さ: プログラムをメモリ上の別の場所に移動させると、命令内のすべてのアドレスを更新する必要があり、再配置が難しくなります。

間接アドレッシング

間接アドレッシングとは、CPUが命令を実行する際、命令に書かれたアドレスそのものではなく、そのアドレスに格納されている値(別のメモリアドレス)を参照して、最終的なデータが格納されている場所(実効アドレス)にアクセスする方式です。これにより、ポインタ(参照)の実装や、メモリの大きな範囲へのアクセスを柔軟に行うことが可能になります。

仕組みの例

- 命令のアドレス部: 命令には「1000番地」という値が含まれているとします。

- 1回目のメモリアクセス: CPUはまず「1000番地」にアクセスします。

- アドレスの取得: 「1000番地」には、データ本体ではなく「1003番地」という別のメモリアドレスが格納されています。

- 2回目のメモリアクセス: CPUは、取得した「1003番地」にアクセスし、そこに格納されているデータ本体を取り出します。

メリット

- ポインタの実装: プログラミングにおけるポインタ(参照)の概念を、ハードウェアレベルで容易に実現できます。

- 柔軟なメモリ操作: プログラムカウンタ(PC)を間接的に利用することで、大きなメモリ領域へのアクセスや、位置独立コード(PIC)の実現に役立ちます。

レジスタ直接アドレッシング

レジスタ直接アドレッシングとは、CPUの命令でデータを直接レジスタ(高速な内部記憶領域)で指定する方式で、実効アドレス計算が不要で非常に高速にデータアクセスできるのが特徴です。命令コードの一部として、対象のデータが格納されているレジスタ(例:AX, BXなど)の「名前」そのものを指定します。

仕組み

- オペランド: 命令のオペランド(データ部分)に、データ本体ではなく「どのレジスタを使うか」という情報(レジスタ名や番号)が書かれています。

- アクセス: CPUは命令を受け取ると、指定されたレジスタに直接アクセスし、その中のデータを読み書きします。外部メモリへのアクセス(メモリアクセス)は発生しません。

- 例:

MOV AX, BX(レジスタBXの内容をレジスタAXにコピーする)のような命令で、AXやBXといったレジスタ名を直接指定します。

特徴

- 高速性: レジスタはCPUに最も近い記憶装置なので、メモリへのアクセスに比べて圧倒的に高速です。

- シンプル: メモリ上のアドレスを計算する必要がないため、命令の実行がシンプルで高速になります。

- 数の制約: CPUが持つレジスタの数には限りがあるため、利用できるレジスタは限られます。

レジスタ間接アドレッシング

レジスタ間接アドレッシングとは、CPUがデータを読み書きする際、命令で直接アドレスを指定せず、「特定のアドレスが格納されているレジスタ」そのものを指定するアドレス指定方式です。レジスタに格納されたアドレス値(ポインタ)を使ってメモリの実際のデータにアクセスするため、柔軟なメモリ操作(ポインタや配列処理、スタック操作など)を可能にし、プログラムの効率と可読性を高めます。

仕組み

- アドレスをレジスタに格納: まず、目的のデータがあるメモリ上のアドレス(番地)を、特定のレジスタ(例: HL, BC, DEレジスタなど)に書き込みます。

- レジスタを間接的に参照: 実際のデータ操作命令(ロード、ストア、加算など)では、そのアドレス値が入っているレジスタ自体を「ポインタ」として指定します。

- 実効アドレスの計算: CPUは指定されたレジスタの内容(アドレス値)を読み出し、それを実効アドレスとしてメモリにアクセスします。

特徴と利点

- ポインタの実装: メモリ上の任意の場所を指すポインタ(参照)を容易に実装できます。

- 配列・構造体処理: ループ処理などで、インクリメント/デクリメントしながら連続するメモリ領域を効率的に処理するのに便利です(自動インクリメント/デクリメント機能と併用されることもあります)。

- 柔軟なメモリ操作: 実行時にアドレスを動的に変更できるため、テーブル参照やスタックの実装、データコピーなどに強力です。

- 再配置可能コード: プログラムカウンタ(PC)をベースレジスタとして使うPC相対アドレッシングは、位置独立コード(PIC)を実現し、メモリ上のどこにロードされても動作するプログラム作成に役立ちます。

インクリメント

変数の値を1増やす操作を指します。

デクリメント

変数の値を1減らす操作を指します。

具体例(Z80プロセッサのイメージ)

LD A, (HL) という命令は、「HLレジスタが指すメモリ番地からデータをAレジスタにロードせよ」という意味になります。

コメント